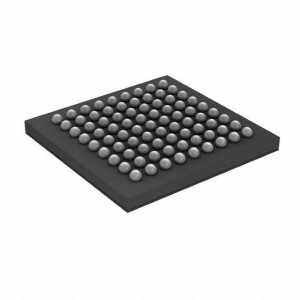

TMS320VC5509AZAY Procesori i kontroleri digitalnog signala – DSP, DSC procesor digitalnog signala s fiksnom točkom 179-NFBGA -40 do 85

♠ Opis proizvoda

| Svojstvo proizvoda | Vrijednost atributa |

| Proizvođač: | Texas Instruments |

| Kategorija proizvoda: | Digitalni procesori signala i kontroleri - DSP, DSC |

| RoHS: | pojedinosti |

| Proizvod: | DSP-ovi |

| Niz: | TMS320VC5509A |

| Stil montaže: | SMD/SMT |

| Paket/kovčeg: | NFBGA-179 |

| Jezgra: | C55x |

| Broj jezgri: | 1 jezgra |

| Maksimalna taktna frekvencija: | 200 MHz |

| L1 Cache memorija instrukcija: | - |

| L1 Cache Memorija podataka: | - |

| Veličina programske memorije: | 64 kB |

| Veličina podatkovnog RAM-a: | 256 kB |

| Radni napon napajanja: | 1,6 V |

| Minimalna radna temperatura: | - 40 C |

| Maksimalna radna temperatura: | + 85 C |

| Ambalaža: | Ladica |

| Marka: | Texas Instruments |

| Vrsta instrukcije: | Fiksna točka |

| Vrsta sučelja: | I2C |

| Osjetljivo na vlagu: | Da |

| Vrsta proizvoda: | DSP - Digitalni signalni procesori i kontroleri |

| Tvornička količina pakiranja: | 160 |

| Potkategorija: | Ugrađeni procesori i kontroleri |

| Napon napajanja - Max: | 1,65 V |

| Napon napajanja - Min.: | 1,55 V |

| Nadzorni mjerači vremena: | Watchdog Timer |

♠ TMS320VC5509A procesor digitalnog signala s fiksnom točkom

TMS320VC5509A procesor digitalnih signala s fiksnom točkom (DSP) temelji se na procesorskoj jezgri CPU generacije TMS320C55x DSP.C55x™ DSP arhitektura postiže visoke performanse i nisku snagu kroz povećani paralelizam i potpuni fokus na smanjenje rasipanja snage.CPU podržava internu strukturu sabirnice koja se sastoji od jedne programske sabirnice, tri sabirnice za čitanje podataka, dvije sabirnice za pisanje podataka i dodatne sabirnice namijenjene periferiji i DMA aktivnostima.Ove sabirnice omogućuju izvođenje do tri čitanja podataka i dva pisanja podataka u jednom ciklusu.Paralelno, DMA kontroler može izvesti do dva prijenosa podataka po ciklusu neovisno o CPU aktivnosti.

C55x CPU nudi dvije multiply-acumulate (MAC) jedinice, svaka sposobna za 17-bitno x 17-bitno množenje u jednom ciklusu.Središnja 40-bitna aritmetičko-logička jedinica (ALU) podržana je dodatnom 16-bitnom ALU.Korištenje ALU-a pod kontrolom je skupa instrukcija, pružajući mogućnost optimizacije paralelne aktivnosti i potrošnje energije.Ovim resursima upravlja se u adresnoj jedinici (AU) i podatkovnoj jedinici (DU) C55x CPU-a.

C55x DSP generacija podržava skup instrukcija promjenjive širine bajta za poboljšanu gustoću koda.Instrukcijska jedinica (IU) izvodi 32-bitno dohvaćanje programa iz unutarnje ili vanjske memorije i stavlja upute u red čekanja za programsku jedinicu (PU).Programska jedinica dekodira upute, usmjerava zadatke na AU i DU resurse i upravlja potpuno zaštićenim cjevovodom.Mogućnost prediktivnog grananja izbjegava ispiranje cjevovoda pri izvršavanju uvjetnih instrukcija.

Funkcije ulaza i izlaza opće namjene i 10-bitni A/D pružaju dovoljno pinova za status, prekide i bit I/O za LCD-e, tipkovnice i medijska sučelja.Paralelno sučelje radi u dva načina, bilo kao podređeno mikrokontroleru koristeći HPI priključak ili kao paralelno medijsko sučelje koristeći asinkroni EMIF.Serijski medij podržan je putem dvije periferije MultiMedia Card/Secure Digital (MMC/SD) i tri McBSP-a.

5509A periferni set uključuje vanjsko memorijsko sučelje (EMIF) koje omogućuje nesmetani pristup asinkronim memorijama kao što su EPROM i SRAM, kao i brzim memorijama visoke gustoće kao što je sinkroni DRAM.Dodatni periferni uređaji uključuju univerzalnu serijsku sabirnicu (USB), sat stvarnog vremena, mjerač vremena, I2C multi-master i slave sučelje.Tri full-duplex višekanalna međuspremnička serijska porta (McBSP) pružaju jednostavno sučelje za niz industrijski standardnih serijskih uređaja i višekanalnu komunikaciju s do 128 odvojeno omogućenih kanala.Poboljšano host-port sučelje (HPI) je 16-bitno paralelno sučelje koje se koristi za pružanje pristupa host procesoru 32K bajta interne memorije na 5509A.HPI se može konfigurirati u multipleksiranom ili nemultipleksiranom načinu rada kako bi se omogućilo sučelje bez lijepljenja širokom spektru host procesora.DMA kontroler osigurava kretanje podataka za šest neovisnih konteksta kanala bez CPU intervencije, osiguravajući DMA protok do dvije 16-bitne riječi po ciklusu.Također su uključena dva mjerača vremena opće namjene, do osam namjenskih I/O pinova opće namjene (GPIO) i generiranje takta digitalne fazno zaključane petlje (DPLL).

5509A podržava nagrađivani eXpressDSP™, Code Composer Studio™ integrirano razvojno okruženje (IDE), DSP/BIOS™, standard algoritma Texas Instrumentsa i najveća mreža treće strane u industriji.Code Composer Studio IDE sadrži alate za generiranje koda uključujući C kompajler i Visual Linker, simulator, RTDX™, XDS510™ upravljačke programe uređaja za emulaciju i module za procjenu.5509A također podržava C55x DSP knjižnica koja sadrži više od 50 temeljnih softverskih jezgri (FIR filtri, IIR filtri, FFT-ovi i razne matematičke funkcije), kao i biblioteke za podršku čipova i ploča.

TMS320C55x DSP jezgra stvorena je s otvorenom arhitekturom koja dopušta dodavanje hardvera specifičnog za aplikaciju za povećanje performansi na određenim algoritmima.Hardverska proširenja na 5509A postižu savršenu ravnotežu performansi fiksne funkcije s programabilnom fleksibilnošću, uz postizanje niske potrošnje energije i cijene koju je tradicionalno bilo teško pronaći na tržištu video procesora.Proširenja omogućuju 5509A da isporuči iznimne performanse video kodeka s više od polovice propusnosti dostupnog za izvođenje dodatnih funkcija kao što su pretvorba prostora boja, operacije korisničkog sučelja, sigurnost, TCP/IP, prepoznavanje glasa i pretvorba teksta u govor.Kao rezultat toga, jedan 5509A DSP može napajati većinu prijenosnih digitalnih video aplikacija s viškom prostora za obradu.Za više informacija pogledajte TMS320C55x Hardware Extensions for Image/Video Applications Programmer's Reference (broj literature SPRU098).Za više informacija o korištenju DSP biblioteke za obradu slike, pogledajte TMS320C55x Biblioteka za obradu slike/video programera Reference (broj literature SPRU037).

• Procesor digitalnog signala TMS320C55x™ visokih performansi male snage i fiksne točke

− 9.26-, 6.95-, 5-ns Vrijeme ciklusa instrukcije

− 108-, 144-, 200-MHz takt

− Jedna/dvije instrukcije izvršene po ciklusu

− Dvostruki množitelji [do 400 milijuna višestrukih akumulacija u sekundi (MMACS)]

− Dvije aritmetičke/logičke jedinice (ALU)

− Tri interne sabirnice za čitanje podataka/operanda i dvije interne sabirnice za pisanje podataka/operanda

• 128K x 16-bitni RAM na čipu, koji se sastoji od:

− 64K bajta RAM-a s dvostrukim pristupom (DARAM) 8 blokova od 4K × 16-bita

− 192K bajta RAM-a s jednim pristupom (SARAM) 24 bloka od 4K × 16-bita

• 64 KB ROM-a na čipu s jednim stanjem čekanja (32 K × 16-bita)

• 8M × 16-bitni maksimalni adresabilni vanjski memorijski prostor (sinkroni DRAM)

• 16-bitna memorija vanjske paralelne sabirnice koja podržava ili:

− Vanjsko memorijsko sučelje (EMIF) s GPIO mogućnostima i Glueless sučeljem za:

− Asinkroni statički RAM (SRAM)

− Asinkroni EPROM

− Sinkroni DRAM (SDRAM)

− 16-bitno paralelno poboljšano Host-Port sučelje (EHPI) s GPIO mogućnostima

• Programabilna kontrola male snage šest funkcionalnih domena uređaja

• Logika emulacije temeljena na skeniranju na čipu

• Periferije na čipu

− Dva 20-bitna mjerača vremena

− Watchdog Timer

− Šestokanalni kontroler izravnog pristupa memoriji (DMA).

− Tri serijska priključka koja podržavaju kombinaciju:

− Do 3 višekanalna serijska ulaza s međuspremnikom (McBSP)

− Do 2 sučelja MultiMedia/Secure Digital Card

− Programabilni generator takta fazno zaključane petlje

− Sedam (LQFP) ili osam (BGA) I/O pinova opće namjene (GPIO) i izlazni pin opće namjene (XF)

− USB pomoćni priključak pune brzine (12 Mbps) koji podržava skupne prijenose, prijenose s prekidima i izokrone prijenose

− Inter-Integrated Circuit (I2C) Multi-Master i Slave sučelje

− Sat stvarnog vremena (RTC) s kristalnim ulazom, zasebnom domenom sata, zasebnim napajanjem

− 4-kanalni (BGA) ili 2-kanalni (LQFP) 10-bitni sukcesivni A/D

• IEEE Std 1149.1† (JTAG) Logika graničnog skeniranja

• Paketi:

− 144-Terminal Low-Profile Quad Flatpack (LQFP) (PGE sufiks)

− 179-Terminal MicroStar BGA™ (Ball Grid Array) (GHH sufiks)

− 179-terminal Lead-Free MicroStar BGA™ (Ball Grid Array) (sufiks ZHH)

• Jezgra 1,2 V (108 MHz), 2,7 V – 3,6 VI/Os

• Jezgra od 1,35 V (144 MHz), 2,7 V – 3,6 VI/Os

• Jezgra 1,6 V (200 MHz), 2,7 V – 3,6 VI/Os

• Hibridni, električni i pogonski sustav (EV/HEV)

– Sustav upravljanja baterijom (BMS)

– Ugrađeni punjač

– Pogonski pretvarač

– DC/DC pretvarač

– Starter/generator